### **General Description**

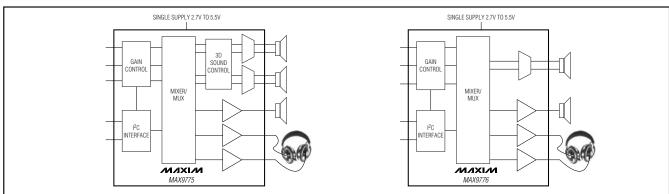

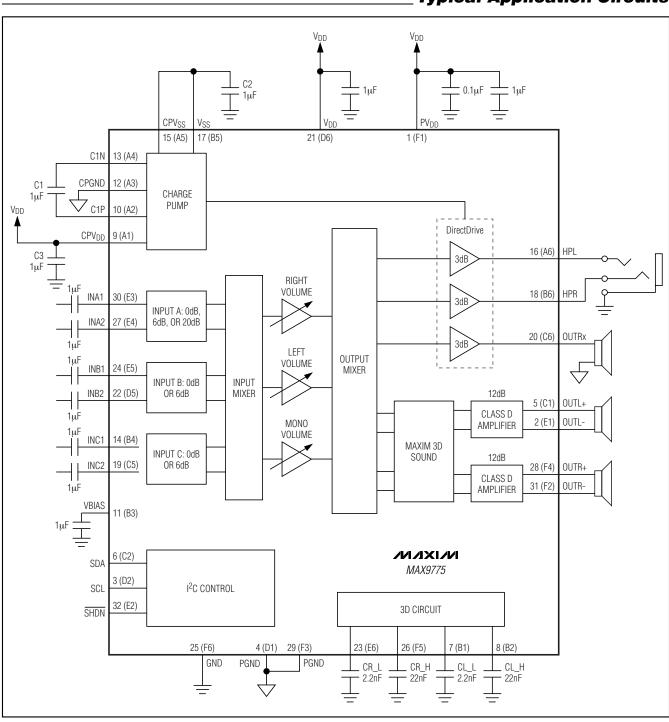

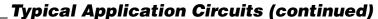

The MAX9775/MAX9776 combine a high-efficiency Class D, stereo/mono audio power amplifier with a mono DirectDrive™ receiver amplifier and a stereo DirectDrive headphone amplifier.

Maxim's 3rd-generation, ultra-low-EMI, Class D audio power amplifiers provide Class AB performance with Class D efficiency. The MAX9775/MAX9776 deliver 1.5W per channel into a  $4\Omega$  load from a 5V supply and offer efficiencies up to 79%. Active emissions limiting circuitry and spread-spectrum modulation greatly reduce EMI, eliminating the need for output filtering found in traditional Class D devices.

The MAX9775/MAX9776 utilize a fully differential architecture, a full-bridged output, and comprehensive click-and-pop suppression. A 3D stereo enhancement function allows the MAX9775 to widen the stereo sound field immersing the listener in a cleaner, richer sound experience than typically found in portable applications. The devices utilize a flexible, user-defined mixer architecture that includes an input mixer, volume control, and output mixer. All control is done through I<sup>2</sup>C.

The mono receiver amplifier and stereo headphone amplifier use Maxim's patented<sup>†</sup> DirectDrive architecture that produces a ground-referenced output from a single supply, eliminating the need for large DC-blocking capacitors, saving cost, space, and component height.

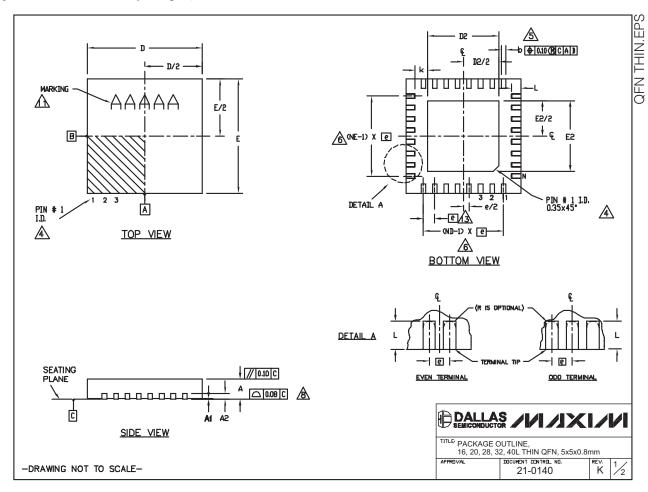

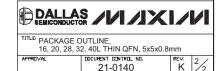

The MAX9775/MAX9776 are available in a 32-pin TQFN (5mm x 5mm) or a 32-bump UCSP $^{TM}$  (3mm x 3mm) package and specified over the extended -40°C to +85°C temperature range.

#### \_Applications

Cell Phones Portable Multimedia Players Handheld Gaming Consoles

†U.S. Patent# 7,061,327

#### Features

- Unique Spread-Spectrum Modulation and Active Emissions Limiting Significantly Reduces EMI

- **♦** 3D Stereo Enhancement (MAX9775 Only)

- ♦ Up to 3 Stereo Inputs

- ♦ 1.5W Stereo Speaker Output (4Ω, V<sub>DD</sub> = 5V)

- ♦ 50mW Mono Receiver/Stereo Headphone Outputs (32Ω, V<sub>DD</sub> = 3.3V)

- ♦ High PSRR (68dB at 217Hz)

- ♦ 79% Efficiency (V<sub>DD</sub> = 3.3V, R<sub>L</sub> = 8Ω, P<sub>OUT</sub> = 470mW)

- ♦ I<sup>2</sup>C Control—Input Configuration, Volume Control, Output Mode

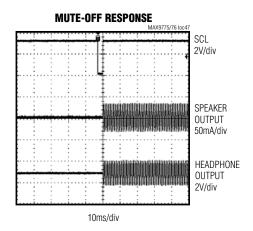

- ♦ Click-and-Pop Suppression

- ♦ Low Total Harmonic Distortion (0.03% at 1kHz)

- **♦ Current-Limit and Thermal Protection**

### **Ordering Information**

| PART          | PIN-<br>PACKAGE | PKG<br>CODE | CLASS D<br>AMPLIFIER |

|---------------|-----------------|-------------|----------------------|

| MAX9775ETJ+*  | 32 TQFN-EP**    | T3255-4     | Stereo               |

| MAX9775EBX+T* | 32 UCSP-32      | B36-4       | Stereo               |

| MAX9776ETJ+   | 32 TQFN-EP**    | T3255-4     | Mono                 |

| MAX9776EBX+T  | 32 UCSP-32      | B36-4       | Mono                 |

**Note:** All devices are specified over the -40°C to +85°C operating temperature range.

- +Denotes lead-free package.

- \*Future product—contact factory for availability.

- \*\*EP = Exposed pad.

#### Pin Configurations appear at end of data sheet.

UCSP is a trademark of Maxim Integrated Products, Inc.

### Simplified Block Diagrams

MIXIM

Maxim Integrated Products

#### **ABSOLUTE MAXIMUM RATINGS**

| VDD to GND         6V           PVDD to PGND         6V           CPVDD to CPGND         6V           CPVop to CPGND         6V |

|---------------------------------------------------------------------------------------------------------------------------------|

| CPVss to CPGND6V to +0.3V<br>Vss to CPGND6V to +0.3V                                                                            |

| C1N(CPV <sub>SS</sub> - 0.3V) to (CPGND + 0.3V)                                                                                 |

| C1P(CPGND - 0.3V) to (CPV <sub>DD</sub> + 0.3V)                                                                                 |

| HPL, HPR to GND( $CPV_{SS}$ - 0.3V) to ( $CPV_{DD}$ + 0.3V)                                                                     |

| GND to PGND and CPGND±0.3V                                                                                                      |

| V <sub>DD</sub> to PV <sub>DD</sub> and CPV <sub>DD</sub> ±0.3V                                                                 |

| SDA, SCL to GND0.3V to +6V                                                                                                      |

| All other pins to GND0.3V to (V <sub>DD</sub> + 0.3V)                                                                           |

| Continuous Current In/Out of PVDD, PGND, CPVDD, CPGND,                                                                          |

| OUT, HPR, and HPL±800mA                                                                                                         |

| Continuous Input Current CPVSS260mA                                                                                             |

| Continuous Input Current (all other pins)±20mA                                                                                  |

| Duration of Short Circuit Between                     |              |

|-------------------------------------------------------|--------------|

| OUT_+ and OUT                                         | Continuous   |

| Duration of HP_, OUT_ Short Circuit to                |              |

| GND or PV <sub>DD</sub>                               | Continuous   |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |              |

| 32-Bump (3mm x 3mm) UCSP Multilayer Board             |              |

| (derate 17.0mW/°C above +70°C)                        | 1360.5mW     |

| 32-Pin (5mm x 5mm) TQFN Single-Layer Board            |              |

| (derate 21.3mW/°C above +70°C)                        | 1702.1mW     |

| 32-Pin TQFN Multilayer Board (derate 34.5mW/°C        |              |

| above +70°C)                                          | 2758.6mW     |

| Junction Temperature                                  | +150°C       |

| Operating Temperature Range40                         | 0°C to +85°C |

| Storage Temperature Range65°                          | °C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C       |

|                                                       |              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = PV_{DD} = CPV_{DD} = 3.3V, GND = PGND = CPGND = 0V, \overline{SHDN} = V_{DD}, I^2C$  settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB,  $\overline{SHDN} = 1$ , SSM = 1). Speaker load resistors (R<sub>LSP</sub>) are terminated between OUT\_+ and OUT\_-, headphone load resistors are terminated to GND, unless otherwise noted. C1 = C2 = C3 = 1 $\mu$ F. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                   | SYMBOL                                                    | CON                                                       | NDITIONS              | MIN  | TYP  | MAX  | UNITS |

|-----------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-----------------------|------|------|------|-------|

| GENERAL                     |                                                           |                                                           |                       |      |      |      |       |

| Supply Voltage Range        | V <sub>DD</sub> , P <sub>VDD</sub> ,<br>C <sub>PVDD</sub> | Inferred from PSRR                                        | test                  | 2.7  |      | 5.5  | V     |

|                             |                                                           | Output mode 1, 6,                                         | 11 (Rx mode)          |      | 6.3  | 10   |       |

| Quiacant Current (Mana)     | loo                                                       | Output mode 4, 9,                                         | 14 (HP mode)          |      | 8    | 12.6 | mA    |

| Quiescent Current (Mono)    | IDD                                                       | Output mode 2, 7,                                         | 12 (SP mode)          |      | 9.5  | 15   | IIIA  |

|                             |                                                           | Output mode 3, 8,                                         | 13 (SP and HP mode)   |      | 12.9 | 18   |       |

| Quiescent Current (Stereo)  |                                                           | Output mode 1, 6,                                         | 11 (Rx mode)          |      | 7    |      |       |

|                             | loo                                                       | Output mode 4, 9,                                         | 14 (HP mode)          |      | 9    |      | mA    |

|                             | IDD                                                       | Output mode 2, 7,                                         |                       | 16.5 | 16.5 |      |       |

|                             |                                                           | Output mode 3, 8,                                         |                       | 20   |      |      |       |

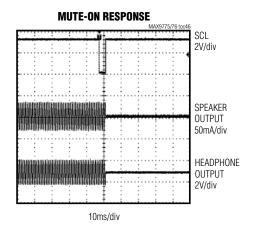

| Mute Current                | I <sub>MUTE</sub>                                         | Current in mute (lov                                      | v power)              |      | 4.7  | 10   | mA    |

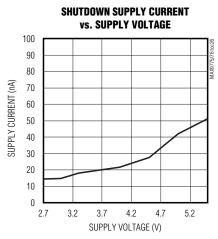

|                             |                                                           | Hard shutdown                                             | SHDN = GND            |      | 0.1  | 10   |       |

| Shutdown Current            | ISHDN                                                     | Soft shutdown                                             |                       | 8.5  | 15   | μΑ   |       |

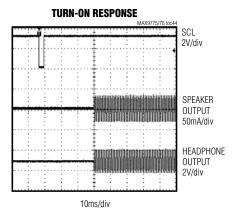

| Turn-On Time                | ton                                                       | Time from shutdown operation                              | n or power-on to full |      | 30   |      | ms    |

| Input Resistance            | R <sub>IN</sub>                                           | B and C pair inputs, T <sub>A</sub> = +25°C,<br>VOL = max |                       | 17.5 | 28   | 41.0 | kΩ    |

|                             |                                                           | A pair inputs, $T_A = +25^{\circ}C$ , $+20dB$             |                       | 3.5  | 5.5  | 8.0  | kΩ    |

| Common-Mode Rejection Ratio | CMRR                                                      | $T_A = +25^{\circ}C$ , $f_{IN} = 1$                       | kHz (Note 2)          | 45   | 50   | 60   | dB    |

| Input DC Bias Voltage       | V <sub>BIAS</sub>                                         | IN_ inputs                                                |                       | 1.12 | 1.25 | 1.38 | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = PV_{DD} = CPV_{DD} = 3.3V, GND = PGND = CPGND = 0V, \overline{SHDN} = V_{DD}, I^2C$  settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB,  $\overline{SHDN} = 1$ , SSM = 1). Speaker load resistors (R<sub>LSP</sub>) are terminated between 0UT\_+ and 0UT\_-, headphone load resistors are terminated to GND, unless otherwise noted. C1 = C2 = C3 = 1 $\mu$ F. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                    | SYMBOL          | CON                                                                 | MIN                                       | TYP | MAX      | UNITS |     |

|----------------------------------------------|-----------------|---------------------------------------------------------------------|-------------------------------------------|-----|----------|-------|-----|

| SPEAKER AMPLIFIERS                           | •               |                                                                     |                                           |     |          |       | •   |

| Outrot Offers Veltere                        | \/              | $T_A = +25$ °C                                                      |                                           |     | ±5.5     | ±23.5 | \/  |

| Output Offset Voltage                        | Vos             | $T_{MIN} \le T_A \le T_{MAX}$                                       |                                           |     |          | ±40   | mV  |

|                                              |                 | Peak voltage,                                                       | Into shutdown                             |     | -62      |       |     |

|                                              | 17              | $T_A = +25^{\circ}C,$                                               | Out of shutdown                           |     | -60      |       | ID. |

| Click-and-Pop Level                          | K <sub>CP</sub> | A-weighted, 32 samples per second                                   | Into mute                                 |     | -63      |       | dB  |

|                                              |                 | (Notes 2, 3)                                                        | Out of mute                               |     | -62      |       | 1   |

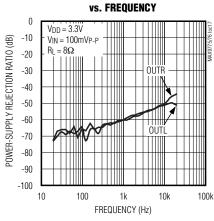

|                                              |                 |                                                                     | $V_{DD} = 2.7V \text{ to } 5.5V$          | 48  | 70       |       |     |

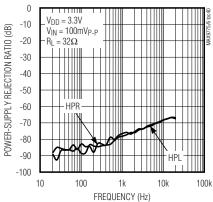

|                                              |                 |                                                                     | f = 217Hz,<br>100mV <sub>P-P</sub> ripple |     | 68       |       |     |

| Power-Supply Rejection Ratio (Note 3)        | PSRR            | T <sub>A</sub> = +25°C                                              | f = 1kHz,<br>100mV <sub>P-P</sub> ripple  |     | 60       |       | dB  |

|                                              |                 |                                                                     | f = 20kHz,<br>100mV <sub>P-P</sub> ripple |     | 50       |       |     |

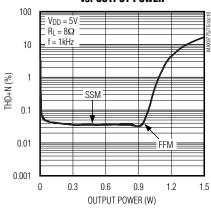

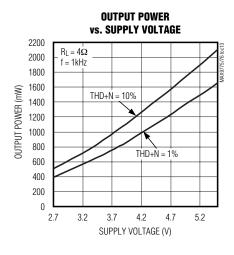

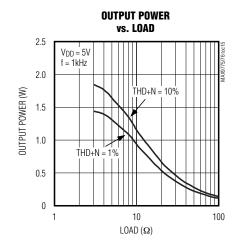

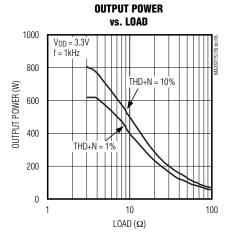

|                                              |                 | TUD N. 40/                                                          | $R_L = 4\Omega$ , $V_{DD} = 5V$           |     | 1500     |       |     |

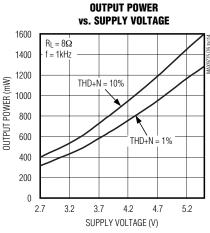

| Output Power (Note 4)                        | Pout            | THD+N = 1%,<br>$T_A = +25^{\circ}C$                                 | $R_L = 8\Omega$ , $V_{DD} = 3.3V$         |     | 450      |       | mW  |

|                                              |                 | TA = +25 0                                                          | $R_L = 8\Omega$ , $V_{DD} = 5V$           |     | 1115     |       |     |

| Current Limit                                |                 |                                                                     |                                           |     | 1.6      |       | А   |

| Total Harmonic Distortion Plus               | THD+N           | f = 1kHz                                                            | $R_L = 8\Omega$ ,<br>$P_{OUT} = 125$ mW   |     | 0.03     |       | %   |

| Noise (Note 4)                               | I HD+N          | I = IKMZ                                                            | $R_L = 4\Omega$ ,<br>$P_{OUT} = 250$ mW   |     | 0.04     |       | 70  |

| Signal-to-Noise Ratio                        | SNR             | $V_{OUT} = 1.8V_{RMS}$ , $R_L = 8\Omega$ , 3D not                   | BW = 20Hz to 20kHz                        |     | 81       |       | dB  |

| 3                                            |                 | active (Note 3)                                                     | A-weighted                                | 84  |          |       |     |

| 0.1.15                                       | ,               | Fixed-frequency mo                                                  | dulation                                  |     | 1100     |       |     |

| Output Frequency                             | fosc            | Spread-spectrum m                                                   | odulation                                 |     | 1100 ±30 |       | kHz |

| Efficiency                                   | η               | P <sub>OUT</sub> = 470mW, f = driven, L = 68µH in s                 |                                           | 79  |          | %     |     |

| Gain                                         | Ay              |                                                                     |                                           | 12  |          | dB    |     |

| Channel-to-Channel Gain<br>Tracking (Note 5) |                 | T <sub>A</sub> = +25°C                                              |                                           |     | ±1       |       | %   |

| 3D Sound Resistors (Note 5)                  | R <sub>3D</sub> | Used with 22nF and capacitors                                       | 5                                         | 7   | 9        | kΩ    |     |

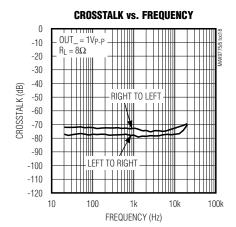

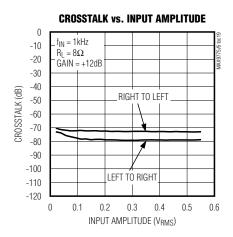

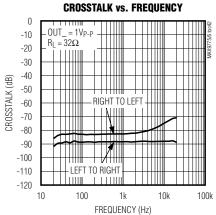

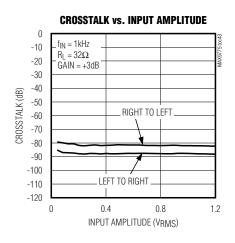

| Crosstalk (Notes 4, 5)                       |                 | L to R, R to L, $f = 10$<br>V <sub>OUT</sub> = 300mV <sub>RMS</sub> |                                           | 73  |          | dB    |     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=PV_{DD}=CPV_{DD}=3.3V,~GND=PGND=CPGND=0V,~\overline{SHDN}=V_{DD},~I^2C$  settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB,  $\overline{SHDN}=1$ , SSM = 1). Speaker load resistors (R<sub>LSP</sub>) are terminated between OUT\_+ and OUT\_-, headphone load resistors are terminated to GND, unless otherwise noted. C1 = C2 = C3 = 1 $\mu$ F. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                             | SYMBOL          | CONDITIONS                                                         |                                           |          | TYP  | MAX  | UNITS |  |

|---------------------------------------|-----------------|--------------------------------------------------------------------|-------------------------------------------|----------|------|------|-------|--|

| RECEIVER AMPLIFIER                    |                 | •                                                                  |                                           |          |      |      | •     |  |

| Output Offset Voltage                 | Vos             | $T_A = +25^{\circ}C$                                               |                                           |          | ±1.8 | ±5.5 | mV    |  |

|                                       |                 | Peak voltage, TA =                                                 | Into shutdown                             |          | -62  |      |       |  |

| Oliah arad Dara Laval                 | IZ :            | +25°C, A-weighted,                                                 | Into mute                                 |          | -67  |      | -10   |  |

| Click-and-Pop Level                   | KCP             | 32 samples per                                                     | Out of shutdown                           |          | -63  |      | dB    |  |

|                                       |                 | second (Notes 3, 6)                                                | Out of mute                               |          | -66  |      |       |  |

|                                       |                 |                                                                    | $V_{DD} = 2.7V \text{ to } 5.5V$          | 58       | 80   |      |       |  |

|                                       |                 |                                                                    | f = 217Hz,<br>100mV <sub>P-P</sub> ripple |          | 80   |      |       |  |

| Power-Supply Rejection Ratio (Note 3) | PSRR            | T <sub>A</sub> = +25°C                                             | f = 1kHz,<br>100mV <sub>P-P</sub> ripple  |          | 70   |      | dB    |  |

|                                       |                 |                                                                    | f = 20kHz,<br>100mV <sub>P-P</sub> ripple |          | 62   |      |       |  |

| 0.1.15                                |                 | $T_A = +25^{\circ}C$ ,                                             | $R_L = 16\Omega$                          |          | 60   |      | 147   |  |

| Output Power                          | Pout            | THD+N = 1%                                                         | $R_L = 32\Omega$                          |          | 50   |      | mW    |  |

| Gain                                  | Ay              |                                                                    |                                           |          |      |      | dB    |  |

| Total Harmonic Distortion Plus        | TUD N           | $R_L = 16\Omega (V_{OUT} = 800 \text{mV}_{RMS}, f = 1 \text{kHz})$ |                                           |          | 0.03 |      | 0/    |  |

| Noise                                 | THD+N           | $R_L = 32\Omega (V_{OUT} = 80)$                                    | 0.024                                     |          |      | %    |       |  |

| O:                                    | CVID            | $R_L = 16\Omega$ , $V_{OUT} =$                                     | BW = 20Hz to 20kHz                        | 87<br>89 |      | -ID  |       |  |

| Signal-to-Noise Ratio                 | SNR             | 800mV <sub>RMS</sub> (Note 3)                                      | A-weighted                                |          |      | dB   |       |  |

| Slew Rate                             | SR              |                                                                    |                                           |          | 0.3  |      | V/µs  |  |

| Capacitive Drive                      | CL              |                                                                    |                                           |          | 300  |      | рF    |  |

| HEADPHONE AMPLIFIERS                  |                 |                                                                    |                                           |          |      |      |       |  |

| Output Offset Voltage                 | Vos             | $T_A = +25^{\circ}C$                                               |                                           |          | ±1.8 | ±5.5 | mV    |  |

|                                       |                 | Peak voltage, T <sub>A</sub> =                                     | Into shutdown                             |          | -61  |      |       |  |

| Click-and-Pop Level                   | K <sub>CP</sub> | +25°C, A-weighted,                                                 | Into mute                                 |          | -65  |      | dB    |  |

| Click-alid-l op Level                 | NCP             | 32 samples per                                                     | Out of shutdown                           |          | -60  |      | ub.   |  |

|                                       |                 | second (Notes 2, 4)                                                | Out of mute                               |          | -64  |      |       |  |

| ESD Protection                        |                 | HP_                                                                | Contact                                   |          | ±4   |      | kV    |  |

| LOD I Totection                       |                 | '"_                                                                | Air                                       |          | ±8   |      | IX V  |  |

|                                       |                 |                                                                    | $V_{DD} = 2.7V \text{ to } 5.5V$          | 58       | 80   |      |       |  |

| Power-Supply Rejection Ratio (Note 3) | PSRR            |                                                                    | f = 217Hz,<br>100mV <sub>P-P</sub> ripple |          | 80   |      | dB    |  |

|                                       |                 | T <sub>A</sub> = +25°C                                             | f = 1kHz,<br>100mV <sub>P-P</sub> ripple  |          | 70   |      |       |  |

|                                       |                 |                                                                    | f = 20kHz,<br>100mV <sub>P-P</sub> ripple |          | 62   |      |       |  |

! \_\_\_\_\_\_ /N/XI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = PV_{DD} = CPV_{DD} = 3.3V, GND = PGND = CPGND = 0V, \overline{SHDN} = V_{DD}, I^2C$  settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB,  $\overline{SHDN} = 1$ , SSM = 1). Speaker load resistors (R<sub>LSP</sub>) are terminated between OUT\_+ and OUT\_-, headphone load resistors are terminated to GND, unless otherwise noted. C1 = C2 = C3 = 1 $\mu$ F. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                            | SYMBOL CONDITIONS |                                                       | MIN                            | TYP | MAX       | UNITS |       |  |

|--------------------------------------|-------------------|-------------------------------------------------------|--------------------------------|-----|-----------|-------|-------|--|

| Output Power                         | Pout              | $T_A = +25^{\circ}C,$                                 | $R_L = 16\Omega$               |     | 60        |       | mW    |  |

| Output Fower                         | FOUT              | THD+N = 1%                                            | THD+N = 1% $R_L = 32\Omega$    |     | 50        |       | 11100 |  |

| Current Limit                        |                   |                                                       |                                |     | 170       |       | mA    |  |

| Gain                                 | Av                |                                                       |                                |     | +3        |       | dB    |  |

| Channel-to-Channel Gain<br>Tracking  |                   | T <sub>A</sub> = +25°C                                |                                |     | ±1        |       | %     |  |

| Total Harmonic Distortion Plus       | THD+N             | $R_L = 16\Omega (V_{OUT} = 80)$                       | 0mV <sub>RMS</sub> , f = 1kHz) |     | 0.03      |       | %     |  |

| Noise                                | I UD+N            | $R_L = 32\Omega (V_{OUT} = 80)$                       | 0mV <sub>RMS</sub> , f = 1kHz) |     | 0.024     |       | 70    |  |

| Signal-to-Noise Ratio                | SNR               | $R_L = 16\Omega$ ,<br>$V_{OUT} = 800 \text{mV}_{RMS}$ | BW = 20Hz to<br>20kHz          |     | 92        |       | dB    |  |

|                                      |                   | V001 = 000111VRIVIS                                   | A-weighted                     |     | 93        |       |       |  |

| Slew Rate                            | SR                |                                                       |                                |     | 0.3       |       | V/µs  |  |

| Capacitive Drive                     | CL                |                                                       |                                |     | 300       |       | рF    |  |

| Crosstalk                            |                   | L to R, R to L, $f = 10k$<br>$V_{OUT} = 160mV_{RMS}$  | Hz, $R_L = 16\Omega$ ,         |     | 75        |       | dB    |  |

| VOLUME CONTROL                       | - 1               | •                                                     |                                |     |           |       |       |  |

|                                      |                   |                                                       | HP gain (max)                  |     | 3         |       |       |  |

|                                      |                   | IN+6dB=0                                              | SP gain (max)                  |     | 12        |       | dB    |  |

|                                      |                   | (minimum gain setting)                                | HP gain (min)                  |     | -72       |       |       |  |

| Volume Control                       |                   |                                                       | SP gain (min)                  |     | -63       |       |       |  |

| Volume Control                       |                   |                                                       | HP gain (max)                  |     | 9         |       |       |  |

|                                      |                   | IN+6dB = 1<br>(maximum gain                           | SP gain (max)                  |     | 18        |       |       |  |

|                                      |                   | setting)                                              | HP gain (min)                  |     | -61       |       |       |  |

|                                      |                   | ,                                                     | SP gain (min)                  |     | -57       |       |       |  |

|                                      |                   | A.I                                                   | Mono+6dB = 0                   |     | 0         |       | Ī     |  |

| Mono Gain                            |                   | All outputs                                           | Mono+6dB = 1                   |     | 6         |       | dB    |  |

| Input Dair A Control                 |                   | INA+20dB = 0 (minim                                   | num gain setting)              | Se  | t by IN+6 | dB    | 40    |  |

| Input Pair A Control                 |                   | INA+20dB = 1 (maxir                                   | num gain setting)              |     | 20        |       | dB    |  |

| Mute Attenuation<br>(Minimum Volume) |                   | V <sub>IN</sub> = 1V <sub>RMS</sub>                   |                                |     | 80        |       | dB    |  |

| DIGITAL INPUTS (SHDN, SDA,           | SCL)              | •                                                     |                                |     |           |       |       |  |

| Input-Voltage High                   | VIH               |                                                       |                                | 1.4 |           |       | V     |  |

| Input-Voltage Low                    | VIL               |                                                       |                                |     |           | 0.4   | V     |  |

| Input Hysteresis (SDA, SCL)          | V <sub>H</sub> YS |                                                       |                                |     | 200       |       | mV    |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = PV_{DD} = CPV_{DD} = 3.3V, GND = PGND = CPGND = 0V, \overline{SHDN} = V_{DD}, I^2C$  settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB,  $\overline{SHDN} = 1$ , SSM = 1). Speaker load resistors (R<sub>LSP</sub>) are terminated between OUT\_+ and OUT\_-, headphone load resistors are terminated to GND, unless otherwise noted. C1 = C2 = C3 = 1 $\mu$ F. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                       | SYMBOL          | CONDITIONS                                                                                          | MIN | TYP | MAX | UNITS |

|-------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| SDA, SCL Input Capacitance                      | CIN             |                                                                                                     |     | 10  |     | рF    |

| Input Leakage Current                           | I <sub>IN</sub> |                                                                                                     |     | 0.3 | 5.0 | μΑ    |

| Pulse Width of Spike Suppressed                 | tsp             |                                                                                                     |     | 50  |     | ns    |

| DIGITAL OUTPUTS (SDA Open D                     | rain)           |                                                                                                     |     |     |     |       |

| Output Low Voltage SDA                          | V <sub>OL</sub> | I <sub>SINK</sub> = 6mA                                                                             |     |     | 0.4 | V     |

| Output Fall Time SDA                            | t <sub>OF</sub> | V <sub>H(MIN)</sub> to V <sub>L(MAX)</sub> bus capacitance = 10pF to 400pF, I <sub>SINK</sub> = 3mA |     | 250 |     | ns    |

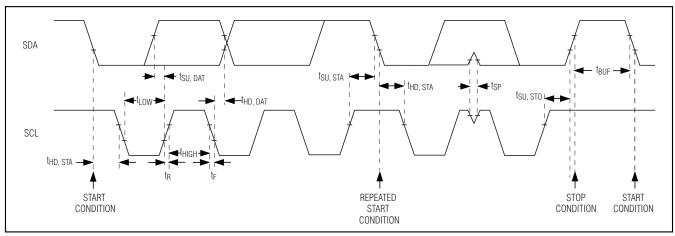

| I <sup>2</sup> C INTERFACE TIMING               |                 |                                                                                                     |     |     |     |       |

| Serial Clock Frequency                          | fscl            |                                                                                                     | DC  |     | 400 | kHz   |

| Bus Free Time Between STOP and START Conditions | tBUF            |                                                                                                     | 1.3 |     |     | μs    |

| START Condition Hold                            | thd:Sta         |                                                                                                     | 0.6 |     |     | μs    |

| STOP Condition Setup Time                       | tsu:sta         |                                                                                                     | 0.6 |     |     | μs    |

| Clock Low Period                                | tLOW            |                                                                                                     | 1.3 |     |     | μs    |

| Clock High Period                               | thigh           |                                                                                                     | 0.6 |     |     | μs    |

| Data Setup Time                                 | tsu:dat         |                                                                                                     | 100 |     |     | ns    |

| Data Hold Time                                  | thd:dat         |                                                                                                     | 0   |     | 900 | ns    |

| Maximum Receive SCL/SDA Rise Time               | t <sub>R</sub>  |                                                                                                     |     |     | 300 | ns    |

| Maximum Receive SCL/SDA Fall Time               | tF              |                                                                                                     |     |     | 300 | ns    |

| Setup Time for STOP Condition                   | tsu:sto         |                                                                                                     | 0.6 |     |     | μs    |

| Capacitive Load for Each Bus<br>Line            | C <sub>b</sub>  |                                                                                                     |     |     | 400 | рF    |

- Note 1: All devices are 100% production tested at room temperature. All temperature limits are guaranteed by design.

- Note 2: Measured at headphone outputs.

- Note 3: Amplifier inputs AC-coupled to GND.

- Note 4: Testing performed with a resistive load in series with an inductor to simulate an actual speaker load. For  $R_L = 8\Omega$ ,  $L = 68\mu H$ ; for  $R_L = 4\Omega$ ,  $L = 47\mu H$ .

- Note 5: MAX9775 only.

- Note 6: Testing performed at room temperature with an 8Ω resistive load in series with a 68μH inductive load connected across BTL outputs for speaker amplifier. Testing performed with a 32Ω resistive load connected between OUT\_ and GND for head-phone amplifier. Testing performed with 32Ω resistive load connected between OUTRx and GND for mono receiver amplifier. Mode transitions are controlled by I<sup>2</sup>C.

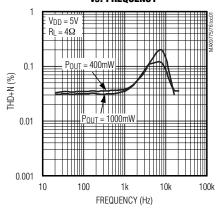

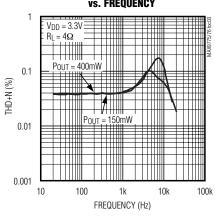

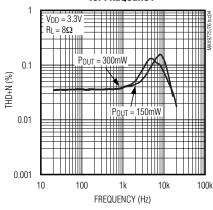

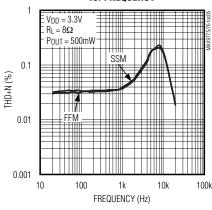

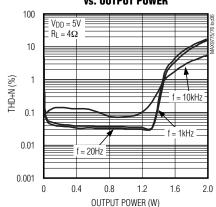

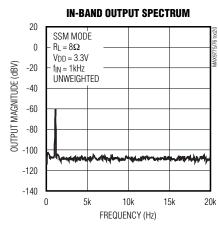

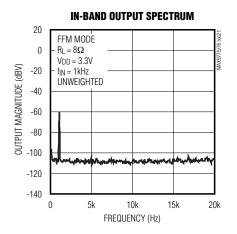

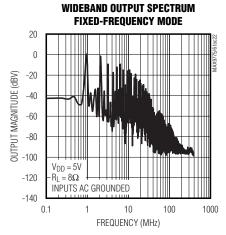

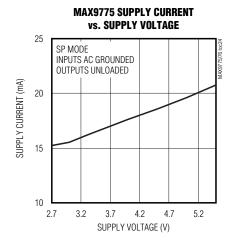

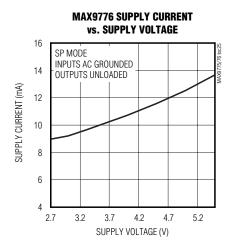

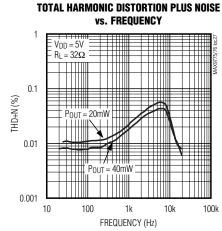

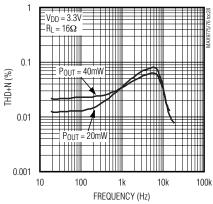

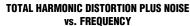

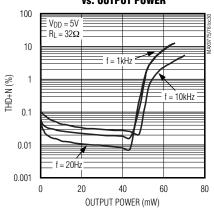

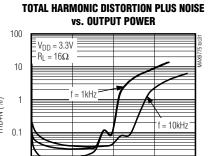

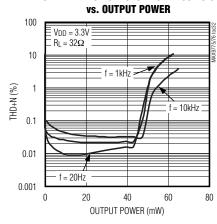

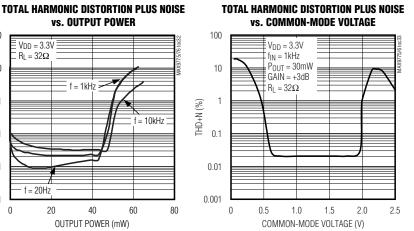

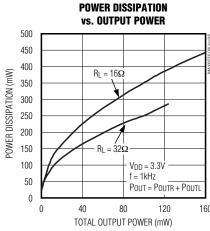

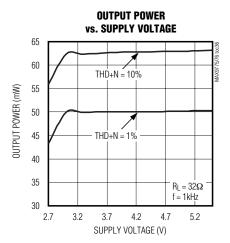

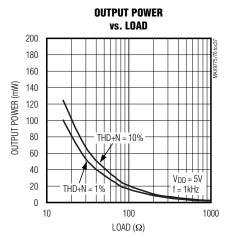

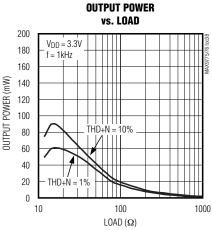

### **Typical Operating Characteristics**

$(V_{DD} = PV_{DD} = CPV_{DD} = 3.3V, GND = PGND = CPGND = 0V, \overline{SHDN} = V_{DD}, I^2C$  default gain settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB,  $\overline{SHDN} = 1$ , SSM = 1). Speaker load resistors (R<sub>LSP</sub>) are terminated between OUT\_+ and OUT\_-, headphone load resistors are terminated to GND, unless otherwise stated. C1 = C2 = C3 = 1 $\mu$ F. T<sub>A</sub> = +25°C, unless otherwise noted.)

## TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency

## TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY

## TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY

## TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency

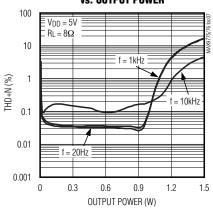

## TOTAL HARMONIC DISTORTION PLUS NOISE vs. Output power

### Typical Operating Characteristics (continued)

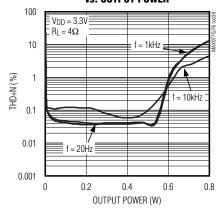

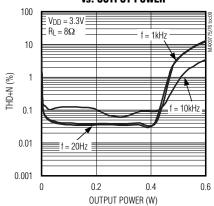

$(V_{DD} = PV_{DD} = CPV_{DD} = 3.3V, \ GND = PGND = CPGND = 0V, \ \overline{SHDN} = V_{DD}, \ I^2C \ default gain settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB, \overline{SHDN} = 1, \overline{SSM} = 1). Speaker load resistors (RLSP) are terminated between OUT_+ and OUT_-, headphone load resistors are terminated to GND, unless otherwise stated. C1 = C2 = C3 = 1<math>\mu$ F. TA = +25°C, unless otherwise noted.)

## TOTAL HARMONIC DISTORTION PLUS NOISE vs. Output power

## TOTAL HARMONIC DISTORTION PLUS NOISE vs. Output Power

### TOTAL HARMONIC DISTORTION PLUS NOISE vs. Output power

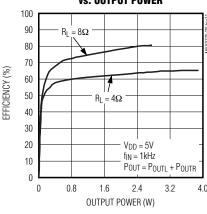

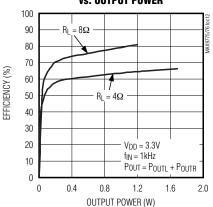

#### EFFICIENCY vs. OUTPUT POWER

### EFFICIENCY vs. OUTPUT POWER

### Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = CPV_{DD} = 3.3V, GND = PGND = CPGND = 0V, \overline{SHDN} = V_{DD}, I^2C$  default gain settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB,  $\overline{SHDN} = 1$ , SSM = 1). Speaker load resistors (R<sub>LSP</sub>) are terminated between OUT\_+ and OUT\_-, headphone load resistors are terminated to GND, unless otherwise stated. C1 = C2 = C3 = 1 $\mu$ F. T<sub>A</sub> = +25°C, unless otherwise noted.)

**POWER-SUPPLY REJECTION RATIO**

### Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = CPV_{DD} = 3.3V, GND = PGND = CPGND = 0V, \overline{SHDN} = V_{DD}, I^2C$  default gain settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB,  $\overline{SHDN} = 1$ , SSM = 1). Speaker load resistors (R<sub>LSP</sub>) are terminated between OUT\_+ and OUT\_-, headphone load resistors are terminated to GND, unless otherwise stated. C1 = C2 = C3 = 1 $\mu$ F. T<sub>A</sub> = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = CPV_{DD} = 3.3V, GND = PGND = CPGND = 0V, \overline{SHDN} = V_{DD}, I^2C$  default gain settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB,  $\overline{SHDN} = 1$ , SSM = 1). Speaker load resistors (R<sub>LSP</sub>) are terminated between OUT\_+ and OUT\_-, headphone load resistors are terminated to GND, unless otherwise stated. C1 = C2 = C3 = 1 $\mu$ F. T<sub>A</sub> = +25°C, unless otherwise noted.)

## TOTAL HARMONIC DISTORTION PLUS NOISE vs. Output Power

0.01

0.001

## 2 x 1.5W, Stereo Class D Audio Subsystem with DirectDrive Headphone Amplifier

### Typical Operating Characteristics (continued)

(VDD = PVDD = CPVDD = 3.3V, GND = PGND = CPGND = 0V, SHDN = VDD, 12C default gain settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB, \$\overline{SHDN}\$ = 1, SSM = 1). Speaker load resistors (RLSP) are terminated between OUT\_+ and OUT\_-, headphone load resistors are terminated to GND, unless otherwise stated. C1 = C2 = C3 = 1µF, TA = +25°C, unless otherwise noted.)

OUTPUT POWER (mW)

120

### Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = CPV_{DD} = 3.3V, GND = PGND = CPGND = 0V, \overline{SHDN} = V_{DD}, I^2C$  default gain settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB,  $\overline{SHDN} = 1$ , SSM = 1). Speaker load resistors (R<sub>LSP</sub>) are terminated between OUT\_+ and OUT\_-, headphone load resistors are terminated to GND, unless otherwise stated. C1 = C2 = C3 = 1 $\mu$ F. T<sub>A</sub> = +25°C, unless otherwise noted.)

## POWER-SUPPLY REJECTION RATIO vs. Frequency

### Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = CPV_{DD} = 3.3V, GND = PGND = CPGND = 0V, \overline{SHDN} = V_{DD}, I^2C$  default gain settings (INA gain = +20dB, INB gain = INC gain = 0dB, volume setting = 0dB, mono path gain = 0dB,  $\overline{SHDN} = 1$ , SSM = 1). Speaker load resistors (R<sub>LSP</sub>) are terminated between OUT\_+ and OUT\_-, headphone load resistors are terminated to GND, unless otherwise stated. C1 = C2 = C3 = 1 $\mu$ F. T<sub>A</sub> = +25°C, unless otherwise noted.)

\_\_ /VI/XI/VI

### Pin Description—MAX9775

| PIN   |        |                   | FUNCTION                                                                                                                                                                                                                                   |  |  |  |  |  |

|-------|--------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TQFN  | UCSP   | NAME              | FUNCTION                                                                                                                                                                                                                                   |  |  |  |  |  |

| 1     | F1     | $PV_{DD}$         | Class D Power Supply                                                                                                                                                                                                                       |  |  |  |  |  |

| 2     | E1     | OUTL-             | Negative Left-Speaker Output                                                                                                                                                                                                               |  |  |  |  |  |

| 3     | D2     | SCL               | Serial Clock Input. Connect a 1kΩ pullup resistor from SCL to V <sub>DD</sub> .                                                                                                                                                            |  |  |  |  |  |

| 4, 29 | D1, F3 | PGND              | Power Ground                                                                                                                                                                                                                               |  |  |  |  |  |

| 5     | C1     | OUTL+             | Positive Left-Speaker Output                                                                                                                                                                                                               |  |  |  |  |  |

| 6     | C2     | SDA               | Serial Data Input. Connect a 1kΩ pullup resistor from SDA to V <sub>DD</sub> .                                                                                                                                                             |  |  |  |  |  |

| 7     | B1     | CL_L              | 3D External Capacitor 3. Connect a 22nF capacitor to GND.                                                                                                                                                                                  |  |  |  |  |  |

| 8     | B2     | CL_H              | 3D External Capacitor 4. Connect a 22nF capacitor to GND.                                                                                                                                                                                  |  |  |  |  |  |

| 9     | A1     | CPV <sub>DD</sub> | Charge-Pump Power Supply                                                                                                                                                                                                                   |  |  |  |  |  |

| 10    | A2     | C1P               | Charge-Pump Flying Capacitor Positive Terminal                                                                                                                                                                                             |  |  |  |  |  |

| 11    | В3     | VBIAS             | Common-Mode Bias                                                                                                                                                                                                                           |  |  |  |  |  |

| 12    | А3     | CPGND             | Charge-Pump GND                                                                                                                                                                                                                            |  |  |  |  |  |

| 13    | A4     | C1N               | Charge-Pump Flying Capacitor Negative Terminal                                                                                                                                                                                             |  |  |  |  |  |

| 14    | B4     | INC1              | Input C1. Left input or positive input (see Table 5a).                                                                                                                                                                                     |  |  |  |  |  |

| 15    | A5     | CPVss             | Charge-Pump Output. Connect to VSS.                                                                                                                                                                                                        |  |  |  |  |  |

| 16    | A6     | HPL               | Left Headphone Output                                                                                                                                                                                                                      |  |  |  |  |  |

| 17    | B5     | Vss               | Headphone Amplifier Negative Power Supply. Connect to CPVSS.                                                                                                                                                                               |  |  |  |  |  |

| 18    | В6     | HPR               | Right Headphone Output                                                                                                                                                                                                                     |  |  |  |  |  |

| 19    | C5     | INC2              | Input C2. Right input or negative input (see Table 5a).                                                                                                                                                                                    |  |  |  |  |  |

| 20    | C6     | OUTRx             | Mono Receiver Output                                                                                                                                                                                                                       |  |  |  |  |  |

| 21    | D6     | $V_{DD}$          | Analog Power Supply                                                                                                                                                                                                                        |  |  |  |  |  |

| 22    | D5     | INB2              | Input B2. Right input or negative input (see Table 5a).                                                                                                                                                                                    |  |  |  |  |  |

| 23    | E6     | CR_L              | 3D External Capacitor 1. Connect a 22nF capacitor to GND.                                                                                                                                                                                  |  |  |  |  |  |

| 24    | E5     | INB1              | Input B1. Left input or positive input (see Table 5a).                                                                                                                                                                                     |  |  |  |  |  |

| 25    | F6     | GND               | Analog Ground                                                                                                                                                                                                                              |  |  |  |  |  |

| 26    | F5     | CR_H              | 3D External Capacitor 2. Connect a 22nF capacitor to GND.                                                                                                                                                                                  |  |  |  |  |  |

| 27    | E4     | INA2              | Input A2. Right input or negative input (see Table 5a).                                                                                                                                                                                    |  |  |  |  |  |

| 28    | F4     | OUTR+             | Positive Right Speaker Output                                                                                                                                                                                                              |  |  |  |  |  |

| 30    | E3     | INA1              | Input A1. Left input or positive input (see Table 5a).                                                                                                                                                                                     |  |  |  |  |  |

| 31    | F2     | OUTR-             | Negative Right Speaker Output                                                                                                                                                                                                              |  |  |  |  |  |

| 32    | E2     | SHDN              | Active-Low Hardware Shutdown                                                                                                                                                                                                               |  |  |  |  |  |

| EP    | _      | EP                | Exposed Pad. The external pad lowers the package's thermal impedance by providing a direct heat conduction path from the die to the PCB. The exposed pad is internally connected to GND. Connect the exposed thermal pad to the GND plane. |  |  |  |  |  |

### Pin Description—MAX9776

| PI                      | N                            |                   | FUNCTION                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|-------------------------|------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TQFN                    | UCSP                         | NAME              | FUNCTION                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 1                       | F1                           | $PV_{DD}$         | Class D Power Supply                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 2                       | E1                           | OUT-              | Negative Left-Speaker Output                                                                                                                                                                                                               |  |  |  |  |  |  |

| 3                       | D2                           | SCL               | Serial Clock Input. Connect a $1k\Omega$ pullup resistor from SCL to $V_{DD}$ .                                                                                                                                                            |  |  |  |  |  |  |

| 4, 29                   | D1, F3                       | PGND              | Power Ground                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 5                       | C1                           | OUT+              | Positive Left-Speaker Output                                                                                                                                                                                                               |  |  |  |  |  |  |

| 6                       | C2                           | SDA               | Serial Data Input. Connect a 1kΩ pullup resistor from SDA to V <sub>DD</sub> .                                                                                                                                                             |  |  |  |  |  |  |

| 7, 8, 23,<br>26, 28, 31 | B1, B2,<br>E6, F2,<br>F4, F5 | I.C.              | Internal Connection. Leave unconnected. This pin is internally connected to the signal path.  Do not connect together or to any other pin.                                                                                                 |  |  |  |  |  |  |

| 9                       | A1                           | CPV <sub>DD</sub> | Charge-Pump Power Supply                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 10                      | A2                           | C1P               | Charge-Pump Flying Capacitor Positive Terminal                                                                                                                                                                                             |  |  |  |  |  |  |

| 11                      | В3                           | VBIAS             | Common-Mode Bias                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 12                      | А3                           | CPGND             | Charge-Pump GND                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 13                      | A4                           | C1N               | Charge-Pump Flying Capacitor Negative Terminal                                                                                                                                                                                             |  |  |  |  |  |  |

| 14                      | B4                           | INC1              | Input C1. Left input or positive input (see Table 5a).                                                                                                                                                                                     |  |  |  |  |  |  |

| 15                      | A5                           | CPVSS             | Charge-Pump Output. Connect to VSS.                                                                                                                                                                                                        |  |  |  |  |  |  |

| 16                      | A6                           | HPL               | Left Headphone Output                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 17                      | B5                           | V <sub>SS</sub>   | Headphone Amplifier Negative Power Supply. Connect to CPVSS.                                                                                                                                                                               |  |  |  |  |  |  |

| 18                      | В6                           | HPR               | Right Headphone Output                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 19                      | C5                           | INC2              | Input C2. Right input or negative input (see Table 5a).                                                                                                                                                                                    |  |  |  |  |  |  |

| 20                      | C6                           | OUTRx             | Mono Receiver Output                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 21                      | D6                           | $V_{DD}$          | Analog Power Supply                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 22                      | D5                           | INB2              | Input B2. Right input or negative input (see Table 5a).                                                                                                                                                                                    |  |  |  |  |  |  |

| 24                      | E5                           | INB1              | Input B1. Left input or positive input (see Table 5a).                                                                                                                                                                                     |  |  |  |  |  |  |

| 25                      | F6                           | GND               | Analog Ground                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 27                      | E4                           | INA2              | Input A2. Right input or negative input (see Table 5a).                                                                                                                                                                                    |  |  |  |  |  |  |

| 30                      | E3                           | INA1              | Input A1. Left input or positive input (see Table 5a).                                                                                                                                                                                     |  |  |  |  |  |  |

| 32                      | E2                           | SHDN              | Active-Low Hardware Shutdown                                                                                                                                                                                                               |  |  |  |  |  |  |

| EP                      | _                            | EP                | Exposed Pad. The external pad lowers the package's thermal impedance by providing a direct heat conduction path from the die to the PCB. The exposed pad is internally connected to GND. Connect the exposed thermal pad to the GND plane. |  |  |  |  |  |  |

### **Typical Application Circuits**

### **Detailed Description**

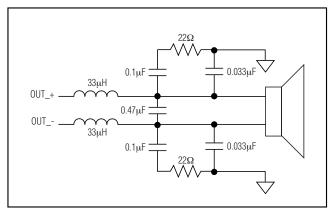

The MAX9775/MAX9776 ultra-low-EMI, filterless, Class D audio power amplifiers feature several improvements to switch-mode amplifier technology. The MAX9775/MAX9776 feature active emissions limiting circuitry to reduce EMI. Zero dead-time technology maintains state-of-the-art efficiency and THD+N performance by allowing the output FETs to switch simultaneously without cross-conduction. A unique filterless modulation scheme and spread-spectrum modulation create compact, flexible, low-noise, efficient audio power amplifiers while occupying minimal board space. The differential input architecture reduces common-mode noise pickup with or without the use of input-coupling capacitors. The MAX9775/MAX9776 can also be configured as single-ended input amplifiers without performance degradation.

The MAX9775/MAX9776 feature three fully differential input pairs (INA\_, INB\_, INC\_) that can be configured as stereo single-ended or mono differential inputs. I<sup>2</sup>C provides control for input configuration, volume level, and mixer configuration. The MAX9775's 3D enhancement feature widens the stereo sound field to improve stereo imaging when stereo speakers are placed in close proximity.

DirectDrive allows the headphone and mono receiver amplifiers to output ground-referenced signals from a single supply, eliminating the need for large DC-blocking capacitors. Comprehensive click-and-pop suppression minimizes audible transients during the turn-on and turn-off of amplifiers.

#### **Class D Speaker Amplifier**

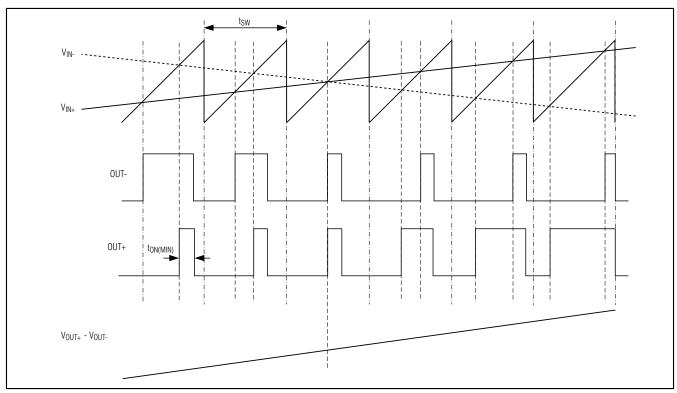

Comparators monitor the audio inputs and compare the complementary input voltages to a sawtooth waveform. The comparators trip when the input magnitude of the sawtooth exceeds their corresponding input voltage. The active emissions limiting circuitry slightly reduces the turn-on rate of the output H-bridge by slew-rate limiting the comparator output pulse. Both comparators reset at a fixed time after the rising edge of the second comparator trip point, generating a minimum-width pulse (ton(MIN), 100ns typ) at the output of the second comparator (Figure 1). As the input voltage increases or decreases, the duration of the pulse at one output increases while the other output pulse duration remains the same. This causes the net voltage across the speaker (VOUT+ - VOUT-) to change. The minimum-width pulse helps the devices to achieve high levels of linearity.

Figure 1. Outputs with an Input Signal Applied

#### **Operating Modes**

#### Fixed-Frequency Modulation

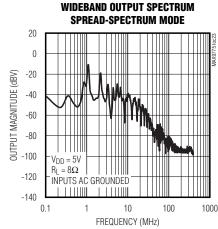

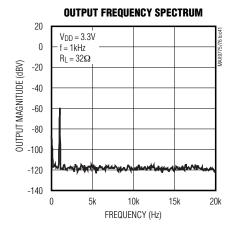

The MAX9775/MAX9776 feature a fixed-frequency modulation mode with a 1.1MHz switching frequency, set through the I<sup>2</sup>C interface (Table 2). In fixed-frequency modulation mode, the frequency spectrum of the Class D output consists of the fundamental switching frequency and its associated harmonics (see the Wideband Output Spectrum Fixed-Frequency Mode graph in the *Typical Operating Characteristics*).

#### Spread-Spectrum Modulation

The MAX9775/MAX9776 feature a unique, patented spread-spectrum modulation that flattens the wideband spectral components. Proprietary techniques ensure that

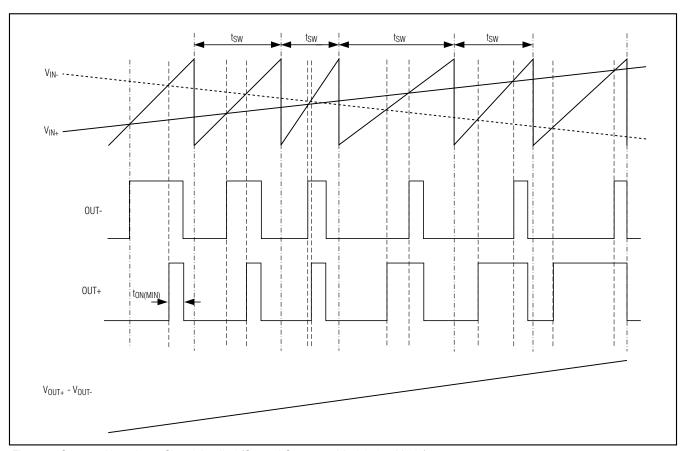

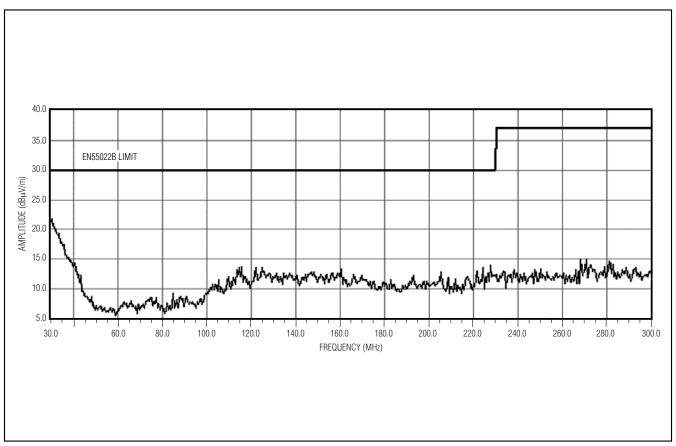

the cycle-to-cycle variation of the switching period does not degrade audio reproduction or efficiency (see the *Typical Operating Characteristics*). Select spread-spectrum modulation mode through the I<sup>2</sup>C interface (Table 2). In spread-spectrum modulation mode, the switching frequency varies randomly by ±30kHz around the center frequency (1.16MHz). The modulation scheme remains the same, but the period of the sawtooth waveform changes from cycle to cycle (Figure 2). Instead of a large amount of spectral energy present at multiples of the switching frequency, the energy is now spread over a bandwidth that increases with frequency. Above a few megahertz, the wideband spectrum looks like white noise for EMI purposes (see Figure 3).

Figure 2. Output with an Input Signal Applied (Spread-Spectrum Modulation Mode)

Figure 3. EMI with 76mm of Speaker Cable

#### Filterless Modulation/Common-Mode Idle

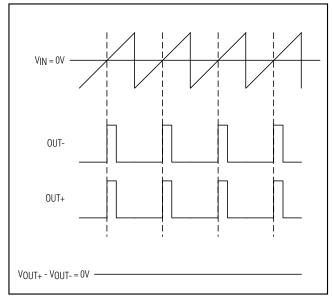

The MAX9775/MAX9776 use Maxim's unique, patented modulation scheme that eliminates the LC filter required by traditional Class D amplifiers, improving efficiency, reducing component count, conserving board space and system cost. Conventional Class D amplifiers output a 50% duty-cycle square wave when no signal is present. With no filter, the square wave appears across the load as a DC voltage, resulting in finite load current, increasing power consumption, especially when idling. When no signal is present at the input of the MAX9775/MAX9776, the outputs switch as shown in Figure 4. Because the MAX9775/MAX9776 drive the speaker differentially, the two outputs cancel each other, resulting in no net idle mode voltage across the speaker, minimizing power consumption.

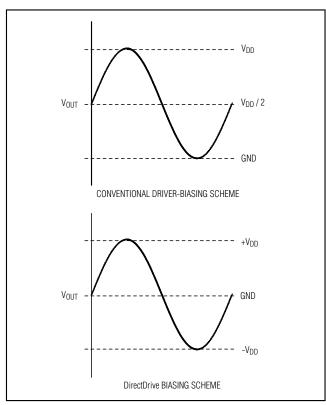

#### **DirectDrive**

Traditional single-supply headphone amplifiers have outputs biased at a nominal DC voltage (typically half the supply) for maximum dynamic range. Large coupling capacitors are needed to block this DC bias from the headphone. Without these capacitors, a significant amount of DC current flows to the headphone, resulting in unnecessary power dissipation and possible damage to both headphone and headphone amplifier.

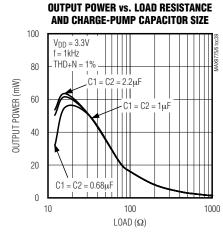

Maxim's patented DirectDrive architecture uses a charge pump to create an internal negative supply voltage. This allows the headphone outputs of the MAX9775/MAX9776 to be biased at GND, almost doubling dynamic range while operating from a single supply. With no DC component, there is no need for the large DC-blocking capacitors. Instead of two large (220µF, typ) tantalum capacitors, the MAX9775/MAX9776 charge pump requires two small ceramic capacitors, conserving board space, reducing cost, and improving the frequency response of the headphone amplifier. See the Output Power vs. Load Resistance and Charge-Pump Capacitor Size graph in the Typical Operating Characteristics for details of the possible capacitor sizes. There is a low DC voltage on the amplifier outputs due to amplifier offset. However, the offset of the MAX9775/MAX9776 is typically 1.4mV, which, when combined with a  $32\Omega$  load, results in less than 44nA of DC current flow to the headphones.

Figure 4. Outputs with No Input Signal

In addition to the cost and size disadvantages of the DC-blocking capacitors required by conventional headphone amplifiers, these capacitors limit the amplifier's low-frequency response and can distort the audio signal. Previous attempts at eliminating the output-coupling capacitors involved biasing the headphone return (sleeve) to the DC bias voltage of the headphone amplifiers. This method raises some issues:

- The sleeve is typically grounded to the chassis.

Using the midrail biasing approach, the sleeve must

be isolated from system ground, complicating product design.

- 2) During an ESD strike, the driver's ESD structures are the only path to system ground. Thus, the amplifier must be able to withstand the full ESD strike.

- 3) When using the headphone jack as a lineout to other equipment, the bias voltage on the sleeve may conflict with the ground potential from other equipment, resulting in possible damage to the amplifiers.

Figure 5. Traditional Amplifier Output vs. MAX9775/MAX9776 DirectDrive Output

#### Charge Pump

The MAX9775/MAX9776 feature a low-noise charge pump. The switching frequency of the charge pump is half the switching frequency of the Class D amplifier, regardless of the operating mode. The nominal switching frequency is well beyond the audio range, and thus does not interfere with the audio signals, resulting in an SNR of 93dB. Although not typically required, additional high-frequency noise attenuation can be achieved by increasing the size of C2 (see the *Typical Application Circuits*). The charge pump is active in both speaker and headphone modes.

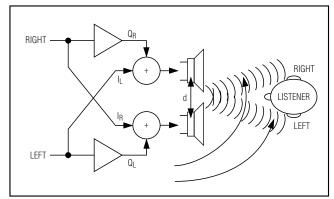

#### 3D Enhancement

The MAX9775 features a 3D stereo enhancement function, allowing the MAX9775 to widen the stereo sound field and immerse the listener in a cleaner, richer sound experience. Note the MAX9776, mono Class D speaker amplifier does not feature 3D stereo enhancement.

As stereo speaker applications become more compact, the quality of stereophonic sound is jeopardized.

Figure 6. MAX9775 3D Stereo Enhancement

With Maxim's 3D stereo enhancement, it is possible to emulate stereo sound in situations where the speakers must be positioned close together. As shown in Figure 6, wave interference can be used to cancel the left channel in the vicinity of the listener's right ear and vice versa. This technique can yield an apparent separation between the speakers that is a factor of four or greater than the actual physical separation.

The external capacitors CL\_L, CL\_H, CR\_L, and CR\_H set the starting and stopping range of the 3D effect. CL\_H and CR\_H are for the lower limit (in the MAX9775 Typical Application Circuit, it is 1kHz), CR\_L and CL\_L are for the higher limit (10kHz). The internal resistor is typically  $7k\Omega$  and the frequencies are calculated as:

$$3D_START = \frac{1}{2\pi RC}$$

where  $R = 7k\Omega$  and  $C = CR_H$  and  $CL_H$ .

$$3D_STOP = \frac{1}{2\pi BC}$$

where  $R = 7k\Omega$  and  $C = CR_L$  and  $CL_L$ .

For example, with  $CR_L = CL_L = 2.2nF$  and  $CR_H = CL_H = 22nF$ , the 3D start frequency is 1kHz and the 3D stop frequency is 10kHz.

Enabling the 3D sound effect results in an apparent 6dB gain because the internal left and right signals are mixed together. This gain can be nulled by volume adjusting the left and right signals. The volume control can be programmed through the I<sup>2</sup>C-compatible interface to compensate for the extra 6dB increase in gain. For example,

if the right and left volume controls are set for a maximum gain 0dB (11111 in Table 7, IN+6dB = 0 from Table 10) before the 3D effect is activated, the volume control should be programmed to -6dB (11001 in Table 7) immediately after the 3D effect has been activated.

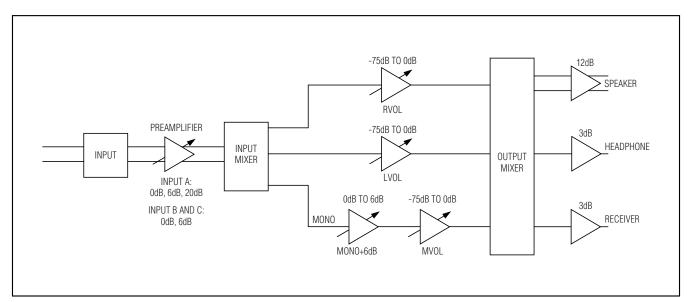

#### Signal Path

The audio inputs of the MAX9775/MAX9776—INA, INB, and INC—are preamplified and then mixed by the input mixer to create three internal signals: Left (L), Right (R), and Mono (M). Tables 5a and 5b show how the inputs are mixed to create L, R, and M. These signals are then independently volume adjusted by the L, R, and M volume control and routed to the output mixer. The output mixer mixes the internal L, R, and M signals to create a variety of audio mixes that are output to the headphone speaker and mono receiver amplifiers. Figure 6 shows the signal path that the audio signals take.

Signal amplification takes place in three stages. In the first stage, the inputs (INA, INB, and INC) are preamplified. The amount by which each input is amplified is determined by the bits INA+20dB (B4 in the Input Mode Control Register) and IN+6dB (B3 in the Global Control Register). After preamplification, they are mixed

in the Input Mixer to create the internal signals L, R, and  ${\sf M}$

In the second stage of amplification, the internal L, R, and M signals are independently volume adjusted.

Finally, each output amplifier has its own internal gain. The speaker, headphone, and mono receiver amplifiers have fixed gains of 12dB, 3dB, and 3dB, respectively.

#### **Current-Limit and Thermal Protection**

The MAX9775/MAX9776 feature current limiting and thermal protection to protect the device from short circuits and overcurrent conditions. The headphone amplifier pulses in the event of an overcurrent condition with a pulse every 100µs as long as the condition is present. Should the current still be high, the above cycle is repeated. The speaker amplifier current-limit protection clamps the output current without shutting down the output. This can result in a distorted output. Current is limited to 1.6A in the speaker amplifiers and 170mA in the headphone and mono receiver amplifiers.

The MAX9775/MAX9776 have thermal protection that disables the device at +150°C until the temperature decreases to +120°C.

Figure 7. Signal Path

#### Click-and-Pop Suppression

In conventional single-supply headphone amplifiers, the output-coupling capacitor is a major contributor of audible clicks and pops. Upon startup, the amplifier charges the coupling capacitor to its bias voltage, typically half the supply. Likewise, during shutdown, the capacitor is discharged to GND. This results in a DC shift across the capacitor, which, in turn, appears as an audible transient at the speaker. Since the MAX9775/MAX9776 headphone amplifier does not require output-coupling capacitors, this problem does not arise.

In most applications, the output of the preamplifier driving the MAX9775/MAX9776 has a DC bias of typically half the supply. During startup, the input-coupling capacitor is charged to the preamplifier's DC bias voltage, resulting in a DC shift across the capacitor and an audible click/pop. An internal delay of 30ms eliminates the click/pop caused by the input filter.

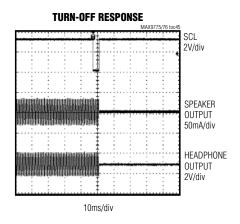

#### Shutdown

The MAX9775/MAX9776 feature a 0.1µA hard shutdown mode that reduces power consumption to extend battery life and a soft shutdown where current consumption is typically 8.5µA. Hard shutdown is controlled by connecting the SHDN pin to GND, disabling the amplifiers, bias circuitry, charge pump, and I<sup>2</sup>C. In shutdown, the headphone amplifier output impedance is  $1.4k\Omega$  and the speaker output impedance is  $300k\Omega$ . Similarly, the MAX9775/MAX9776 enter soft-shutdown when the SHDN bit = 0 (see Table 2). The  $I^2C$  interface is active and the contents of the command register are not affected when in soft-shutdown. This allows the master to write to the MAX9775/MAX9776 while in shutdown. The I<sup>2</sup>C interface is completely disabled in hardware shutdown. When the MAX9775/MAX9776 are re-enabled the default settings are applied (see Table 3).

#### I<sup>2</sup>C Interface

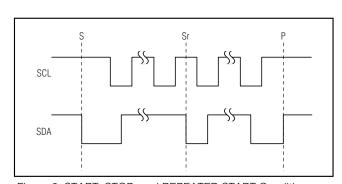

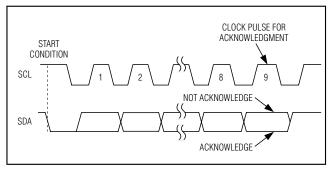

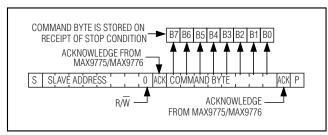

The MAX9775/MAX9776 feature an I<sup>2</sup>C 2-wire serial interface consisting of a serial data line (SDA) and a serial clock line (SCL). SDA and SCL facilitate communication between the MAX9775/MAX9776 and the master at clock rates up to 400kHz. Figure 8 shows the 2-wire interface timing diagram. The MAX9775/MAX9776 are receive-only slave devices relying on the master to generate the SCL signal. The master, typically a microcontroller, generates SCL and initiates data transfer on the bus. The MAX9775/MAX9776 cannot write to the SDA bus except to acknowledge the receipt of data from the master. The MAX9775/MAX9776 will not acknowledge a read command from the master.

A master device communicates to the MAX9775/MAX9776 by transmitting the proper address followed by the data word. Each transmit sequence is framed by a START (S) or REPEATED START (Sr) condition and a STOP (P) condition. Each word transmitted over the bus is 8 bits long and is always followed by an acknowledge clock pulse.